友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com

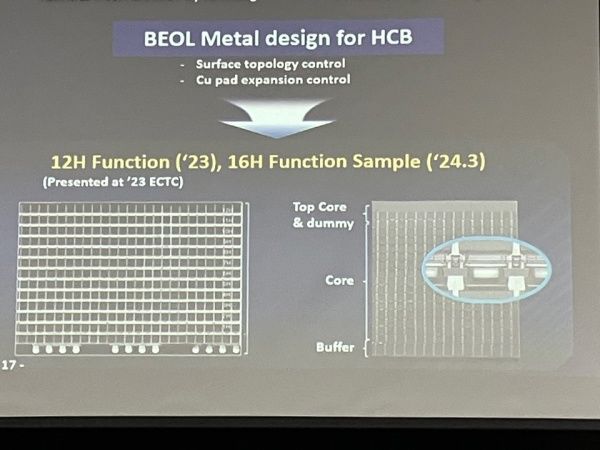

三星完成 16 层混合键合堆叠验证,有望在 HBM4 内存广泛应用

37

0

相关文章

近七日浏览最多

最新文章

标签云

三星

华为

互联网

小手机

手机厂商

市场份额

知名企业

折叠产品线

大陆

台积电

英伟达

中芯国际

芯片代工

芯片制造商

台湾积体电路制造

安卓

苹果手机

华为手机

智能手机

黄仁勋

英特尔

amd

芯片供应

折叠

手机

黑科技

余承东

屏幕铰链

新品发布会

俄罗斯

应用商店

苹果公司

财务会计

财务报表

安卓手机

芯片

路透社

三星电子

ui

android

美光

sk

oled

cmos

苹果

pi

吉利

redmi

lcd

4g

国产品牌

现代汽车

世界500强

dram

pdd

操作系统

小米

soc

gpu

xperia

索尼

魅族

骁龙

pdf

科学家

投资

相机

科技

航空航天

酷睿

硬盘

主机

内存

性价比

处理器

mini

电池容量

宏碁

pilot

巫师3

switch

cpu

v10

原神

nfc

红魔

快科技

联发科天玑

高通

q4

intel

ddr5

联发科

安兔兔

何小鹏

华为云

云空间

摄影

choi

apple

linux

英特尔酷睿

ultra

笔记本电脑

千元机

荣耀play

固态硬盘

联邦法院

asml

光刻机

科创板日报

半导体

etf

权重股

摩根士丹利

国金证券

归母净利润

q3

ds

sk海力士

人工智能

nvme

美元

ddr4

日本

韩国

美国

郭明錤

逮捕

中国

间谍罪

反间谍法

韩国公民

莫迪

印度警方

三星罢工抗议

大屏幕

手机市场

手机行业

卷曲屏手机

华为mate

iphone

交易所

韩国央行

共享单车

雷军

股价

特斯拉

商业内幕

微软

抗议活动

娃哈哈

宗馥莉

小鹏汽车

抖音

清华大学

人均gdp

股票

三星手机